AI 设备进程巨大卷数据真实

但是,许多AI 硬件团队发现早期早期原型表现不同一次工作负载增加。 信号不稳定,间歇性通信错误、和意外延迟尖峰经常出现何时数据带宽达到其操作限制。 这些问题很少引起由处理器本身。 更多通常,他们源自来自董事会-级别设计决策 制作没有完全考虑高速度路由行为。

A 好-结构化高速度数据AI PCBA 解决这些挑战通过对齐信号路由,堆栈向上配置,和制造精度与AI 的实际带宽要求

为什么高-速度数据架构更改PCBA 要求

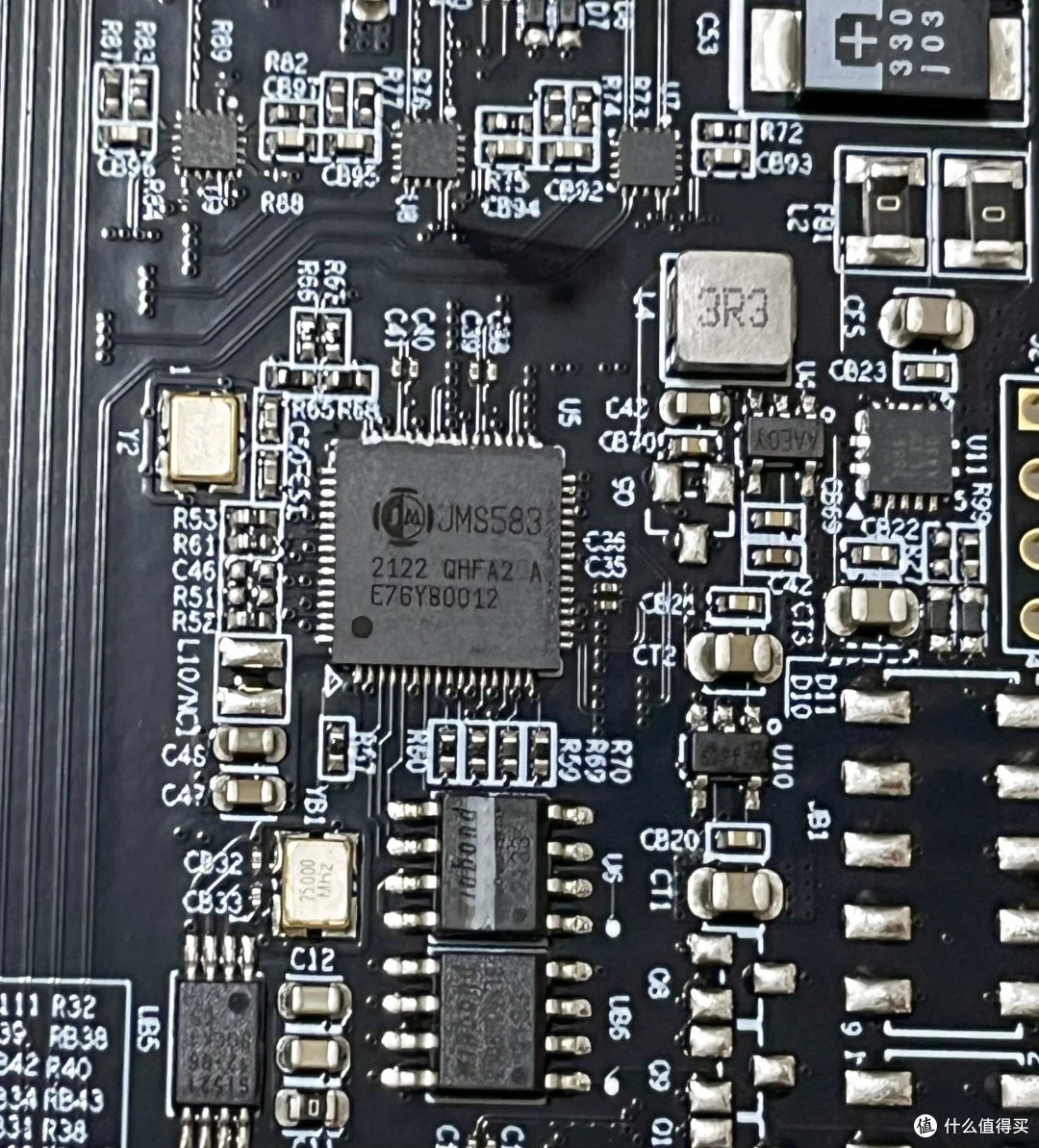

传统嵌入式电子产品经常以中等数据速率操作 哪里小路由缺陷有影响有限。影响。 人工智能系统操作不同。 现代AI 板经常集成接口此类如DDR 内存通道、PCIe 连接、和高速度相机或传感器

在此环境中,甚至小的不一致可以引入信号反射或时序不匹配。 对于示例,一个长度差异仅一几毫米之间差异对可能原因倾斜扰乱数据对齐。 超过时间,此不稳定清单作为间歇性错误是困难重现在基本期间测试。

A 可靠高-速度数据AI PCBA 因此强调严格路由纪律。 受控阻抗走线,仔细匹配差分对,和正确引用地面飞机确保信号以可预测的方式传播跨板。

工程团队实施这些练习经常观察可衡量的改进在通信稳定性,与信号完整性利润增加15–20% 与相比传统路由方法。

<小时数据开始=“3499”数据结束=“3502”>材质和堆栈-向上选择高-速度AI 主板

信号 性能 是 不是 仅由路由几何形状确定。 PCB 材料和堆叠-向上结构还影响数据完整性, 特别是当信号频率上升时以上几个千兆赫。

标准 FR-4 材质 可能执行充分中等-速度电子设备,但是高速度人工智能系统经常好处来自低-损耗层压板。 材料具有a 电介质损耗系数 (Df) 低于 0.005 显着减少信号衰减,允许长高速度轨迹到保持干净波形。

堆栈-向上 规划 正在 同样同样重要。 多层结构—常见排列从六到十二图层—允许设计师单独信号层来自电源和地面飞机。 此分离稳定阻抗和减少电磁干扰相邻之间 痕迹。

当a 高-速度数据AI PCBA 集成优化材质和堆栈-向上架构,系统通常实现两者改进了信号清晰度并且更好EMI 控制,降低可能性重新设计系统集成。

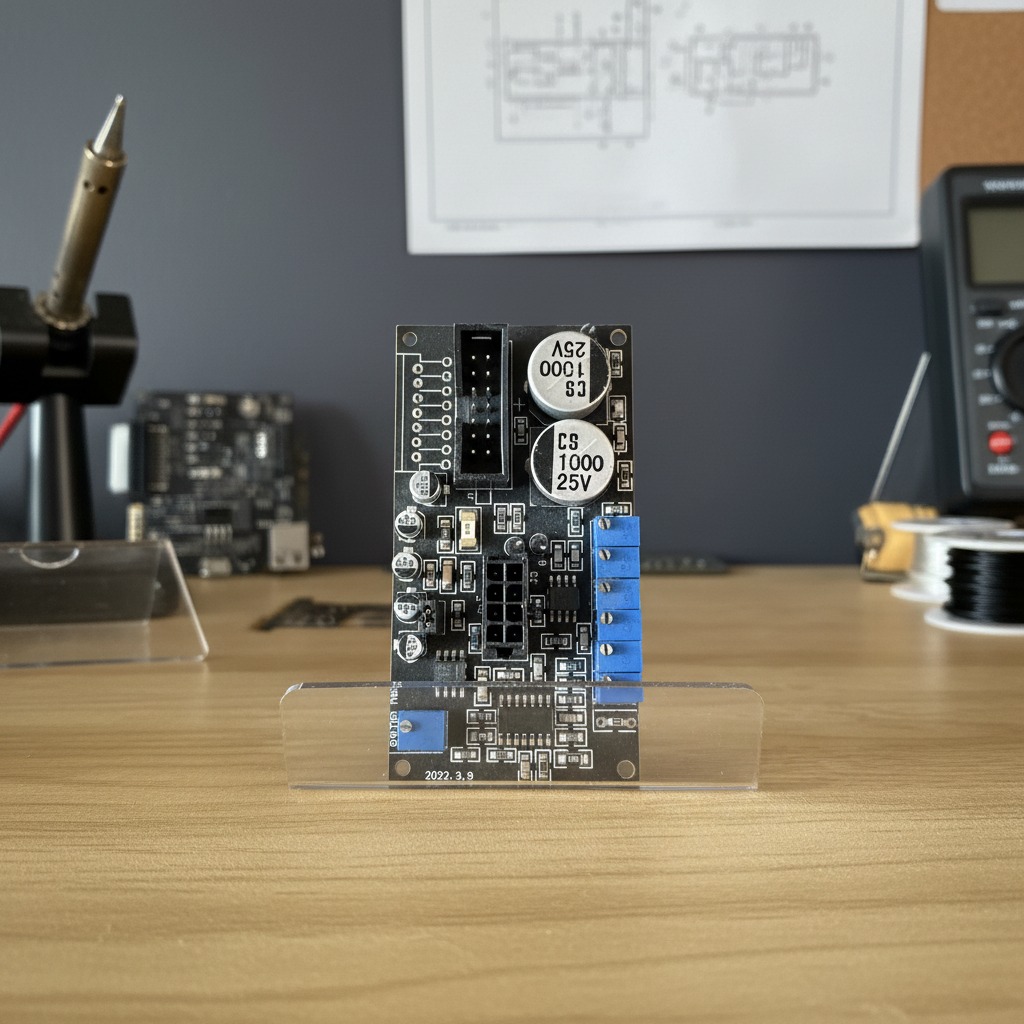

功率密度和热管理中AI 处理板

AI 处理器和加速器在计算

没有 适当的 热规划,热量由这些组件

在实用板设计,热控制涉及更多比只需添加热量水槽。 铜分布跨内部层传播热量横向,同时阵列热敏过孔帮助传输能量远离来自关键组件。

A 良好-设计高速度数据AI PCBA 直接集成这些热力策略直接进入布局阶段。 系统采用平衡铜结构和优化组件放置经常降低峰值热点温度由 10–25°C,显着改进长-术语操作稳定性。

<小时数据开始=“5657”数据结束=“5660”>制造精度和数据可靠性

高速度信号性能可以降级如果装配公差在生产批次之间变化。 轻微差异焊料厚度或组件对齐可以巧妙地更改阻抗特性和引入信号不规则性。

制造纪律因此成为a 关键因素对于AI 硬件生产。 稳定模板设计,准确放置校准,和一致回流焊温度个人资料确保每个董事会保持相同电气行为。

制造因素影响高-速度AI PCBA

| 制造因素 | 控制方法 | 典型结果 | 差分对路由 | 长度匹配 | 减少信号偏斜 | 阻抗控制 | 受控堆栈-向上 | 15–20% 信号完整性改进 | 热铜平衡 | 均匀热量分布 | 较低热点阵型 | 展示位置准确度 | 精细-间距对齐 | 改进信号可靠性 | 流程稳定性 | 受控回流配置文件 | 减少批次变化 |

|---|