AI dispositivos proceso enorme volúmenes de datos en real tiempo. Si el sistema está manejando borde visión procesamiento, neural inferencia, o máquina aprendizaje aceleración, el hardware debe sostener constante altavelocidad comunicación entre procesadores, memoria, y periféricos módulos.

Sin embargo, muchos IA hardware equipos descubren que primeros prototipos comportarse de manera diferente una vez cargas de trabajo aumentar. Señal inestabilidad, intermitente comunicación errores, y inesperada latencia picos a menudo aparece cuando datos ancho de banda alcanza su límite operativo . Estos problemas son raramente causado por el procesador en sí. Más a menudo, ellos se originan de tablero-nivel diseño decisiones que fueron fabricados sin totalmente considerando altavelocidad comportamiento de enrutamiento.

Un bienestructurado altavelocidad datos AI PCBA aborda estos desafíos alineando señal enrutamiento, pila-arriba configuración, y fabricación precisión con el ancho de banda real requisitos de AI sistemas. A través de control optimizado impedancia , controlado capa separación, y ensamblaje preciso procesos, nuestro equipo de ingeniería garantiza que datos vías permanecen estable par bajo sostenido computacional cargar.

Por qué AltaVelocidad Datos Arquitectura Cambios PCBA Requisitos

electrónica tradicional integrada a menudo operar con tarifas moderadas donde pequeñas enrutamiento imperfecciones tienen impacto limitado . Los sistemas IA operan de manera diferente. Tableros IA modernos frecuentemente integrar interfaces tales como memoria DDR canales, PCIe conexiones, y altavelocidad cámara o sensor enlaces. Estas señales viajan en varios gigabits por segundo, que significa traza geometría y enrutamiento simetría conviértete en crítico.

En este entorno, incluso pequeñas inconsistencias pueden introducir señal reflexión o sincronización no coincide. Para ejemplo, una longitud diferencia de sólo unos unos milímetros entre diferencial pares puede causar sesgo que interrumpe la alineación de datos . A lo largo de tiempo, esta inestabilidad se manifiesta como intermitentes errores que son difícil de reproducir durante básico pruebas.

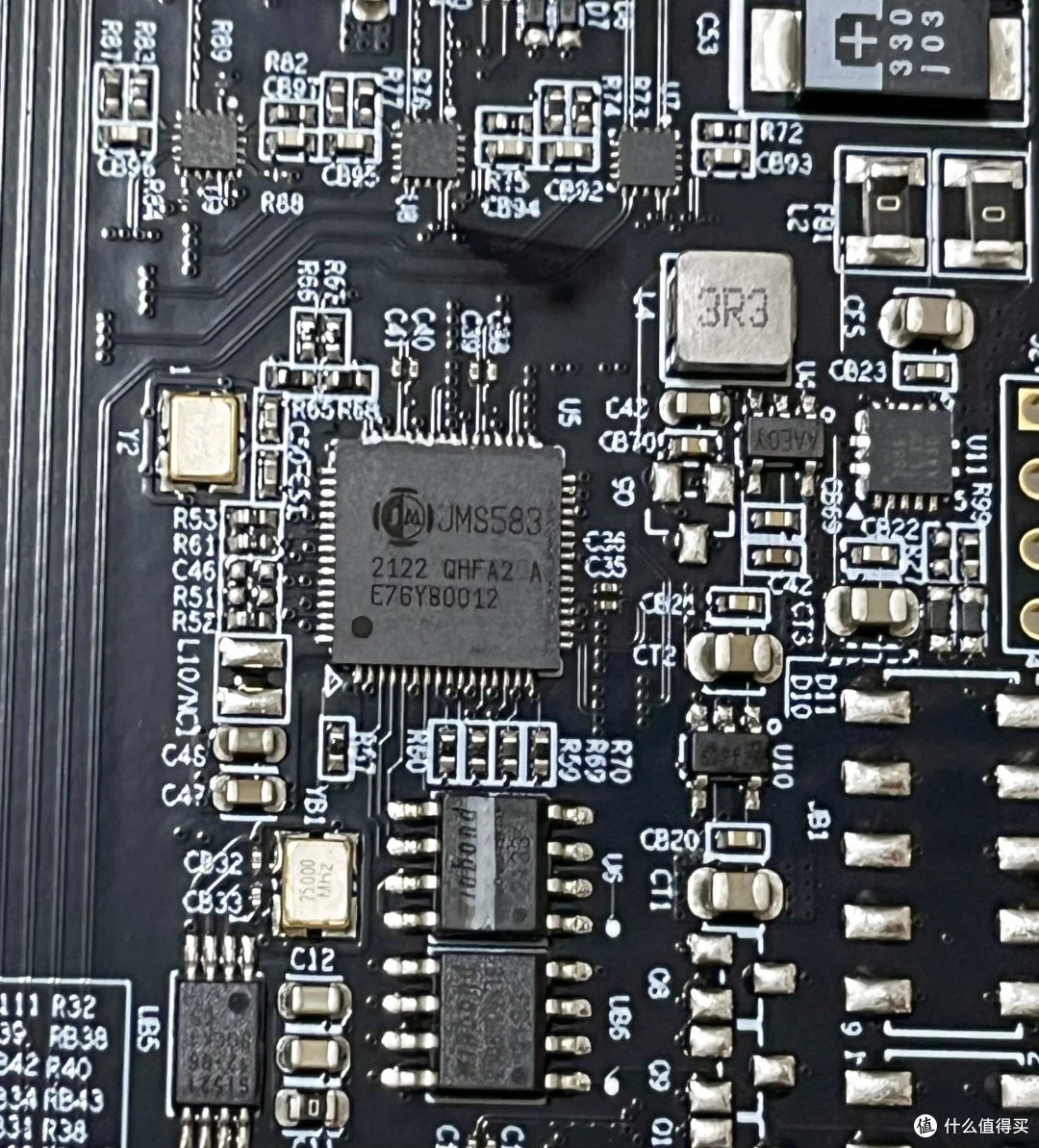

Un confiable altavelocidad datos AI PCBA por lo tanto enfatiza estricta enrutamiento disciplina. Rastros controlados impedancia , cuidadosamente emparejados diferencial pares, y correctamente referenciados tierra aviones asegurar que señales propagar de forma predecible en el tablero.

equipos de ingeniería implementando estos prácticas a menudo observar mejoras medibles en comunicación estabilidad, con señal integridad márgenes aumentando en 15–20% comparado con enfoques enrutamiento convencionales.

Material y Pila-Arriba Opciones para AltaVelocidad AI Tableros

Señal rendimiento es no determinado únicamente por enrutamiento geometría. PCB material y apiladoarriba estructura también influencia datos integridad, particularmente cuando señal las frecuencias aumentan arriba varios gigahercios.

Estándar FR-4 materiales puede realizar adecuadamente para moderado-velocidad electrónica, pero altavelocidad AI sistemas a menudo se benefician de laminados baja pérdida. Materiales con una pérdida dieléctrica factor (Df) abajo 0,005 significativamente reducir señal atenuación, permitiendo larga altavelocidad trazas a mantener limpiar formas de onda.

Apilar-arriba planificación es igualmente importante. estructuras de variascapas estructuras:comúnmente rango de seis a doce capas:permitir diseñadores separar señal capas de potencia y tierra aviones. Esta separación estabiliza impedancia y reduce interferencia electromagnética entre rastros adyacentes.

Cuando a altavelocidad datos AI PCBA integra materiales optimizados y apiladosarriba arquitectura, sistemas a menudo lograr ambos mejorada señal claridad y mejor EMI control, reduciendo la probabilidad de rediseño durante la integración del sistema .

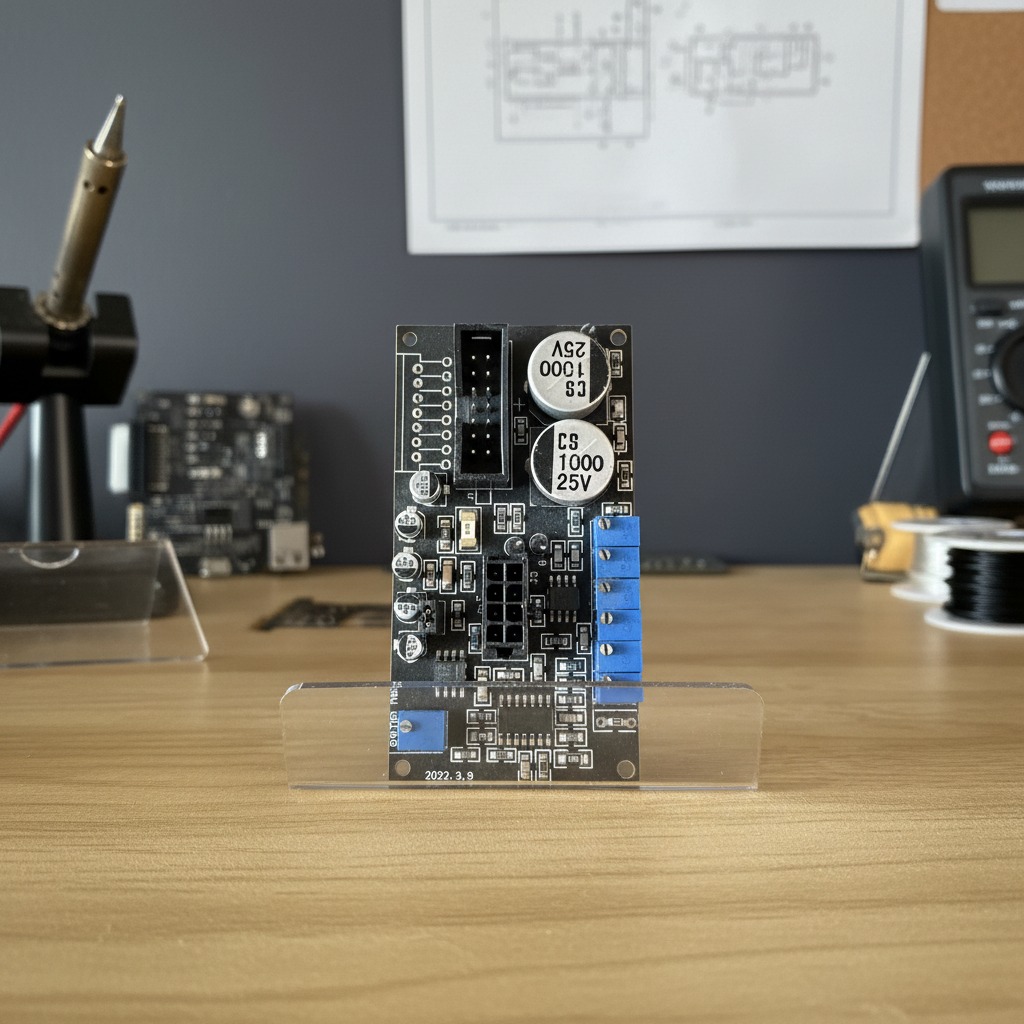

Potencia Densidad y Térmica Gestión en IA Procesamiento Tableros

IA procesadores y aceleradores consume considerable potencia durante cómputo estallidos. Cuando combinado con altavelocidad memoria módulos y interfaces de comunicación , potencia densidad aumenta rápidamente en un área física limitada.

Sin planificación térmica , calor generado por estos componentes puede acumular alrededor de procesamiento clústeres. Elevadas temperaturas degradadas semiconductores eficiencia y puede causar estrangulamiento en AI dispositivos diseñados para cargas de trabajo continuas .

En práctico tablero diseños, control térmico control implica más que simplemente agregando calor disipadores. Cobre distribución entre capas internas difunde calor lateralmente, mientras matrices de térmica vías ayuda transferencia energía lejos de crítico componentes.

Un biendiseñado altavelocidad datos AI PCBA integra estas térmicas estrategias directamente en el diseño escenario. Sistemas que emplean cobre equilibrado estructuras y componente optimizado ubicación a menudo reducir temperaturas máximas punto caliente por 10–25°C, significativamente mejorando largotérmino operacional estabilidad.

Fabricación Precisión y Datos Confiabilidad

altavelocidad señal rendimiento puede degradar si ensamblaje tolerancias varía entre producción lotes. Ligeras diferencias en soldadura espesor o componente alineación puede sutilmente cambiar impedancia características y introducir señal irregularidades.

Fabricación disciplina por lo tanto se convierte un crítico factor para IA hardware producción. Estable plantilla diseño, precisa ubicación calibración, y reflujo consistente temperatura perfiles garantice que cada tablero mantiene la misma eléctrica comportamiento.

Manufacturing Factors Affecting High-Speed AI PCBA

| Manufacturing Factor | Control Method | Typical Result |

|---|---|---|

| Differential pair routing | Length matching | Reduced signal skew |

| Impedance control | Controlled stack-up | 15–20% signal integrity improvement |

| Thermal copper balancing | Even heat distribution | Lower hotspot formation |

| Placement accuracy | Fine-pitch alignment | Improved signal reliability |

| Process stability | Controlled reflow profile | Reduced batch variation |